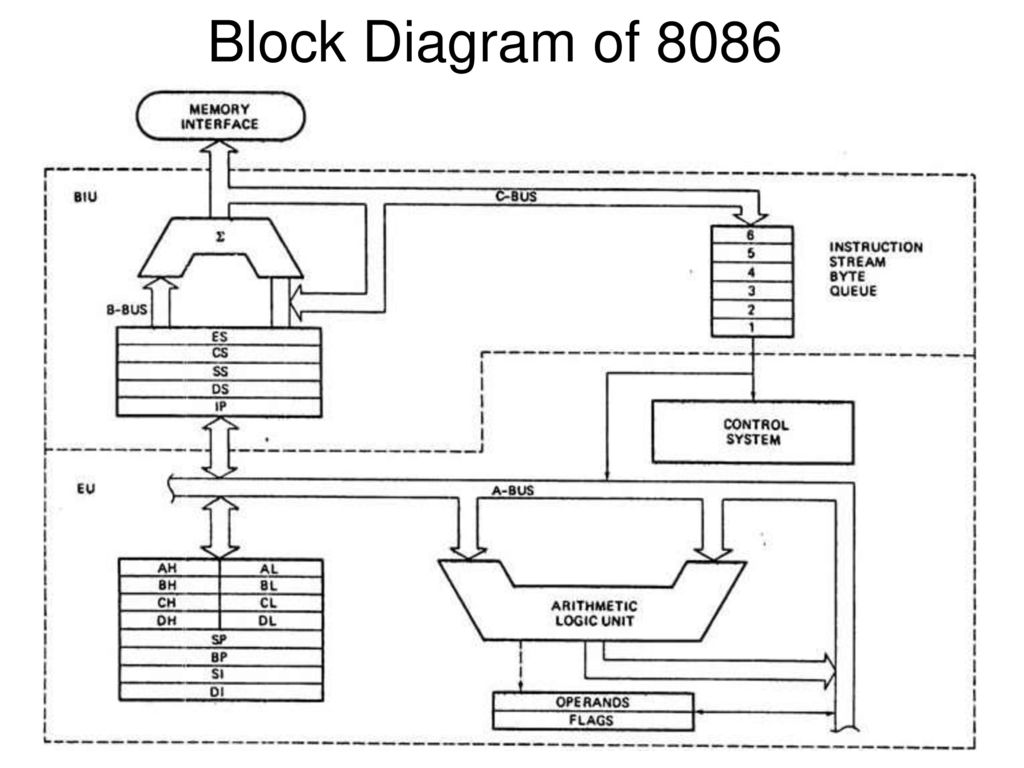

8086 CPU ARCHITECTUREThe microprocessorsfunctions as the CPU in the stored program model of the digital computer. Itsjob is to generate all system timing signals and synchronize the transfer of databetween memory, I/O, and itself. It accomplishes this task via the three-bussystem architecture previously discussed.The microprocessor alsohas a S/W function. It must recognize, decode, andexecute program instructions fetched from the memory unit. This requires anArithmetic-Logic Unit (ALU) within the CPU to perform arithmetic and logical(AND, OR, NOT, compare, etc) functions.The 8086 CPU is organizedas two separate processors, called the Bus Interface Unit (BIU) and theExecution Unit (EU).

The BIU provides H/W functions, including generation ofthe memory and I/O addresses for the transfer of data between the outside world-outside the CPU, that is- and the EU.The EU receives programinstruction codes and data from the BIU, executes these instructions, and storethe results in the general registers. By passing the data back to the BIU, datacan also be stored in a memory location or written to an output device. Notethat the EU has no connection to the system buses.

It receives and outputs allits data thru the BIU.The only differencebetween an 8088 microprocessor and an 8086 microprocessor is the BIU. In the8088, the BIU data bus path is 8 bits wide versus the 8086's 16-bit data bus.Another difference is that the 8088 instruction queue is four bytes longinstead of six.The important point tonote, however, is that because the EU is the same for each processor, theprogramming instructions are exactly the same for each. Programs written forthe 8086 can be run on the 8088 without any changes.FETCH AND EXECUTEAlthough the 8086/88still functions as a stored program computer, organization of the CPU into aseparate BIU and EU allows the fetch and execute cycles to overlap. To seethis, consider what happens when the 8086 or 8088 is first started.1.

The BIU outputs thecontents of the instruction pointer register (IP) onto the address bus, causingthe selected byte or word to be read into the BIU.2. Register IP is incremented by 1 to prepare for the next instruction fetch.3. Once inside the BIU, the instruction is passed to the queue. This is afirst-in, first-out storage register sometimes likened to a'pipeline'.4. Assuming that the queue is initially empty, the EU immediately draws thisinstruction from the queue and begins execution.5. While the EU is executing this instruction, the BIU proceeds to fetch a newinstruction.

Depending on the execution time of the first instruction, the BIUmay fill the queue with several new instructions before the EU is ready to drawits next instruction.The BIU is programmed tofetch a new instruction whenever the queue has room for one (with the 8088) ortwo (with the 8086) additional bytes. The advantage of this pipelinedarchitecture is that the EU can execute instructions almost continually insteadof having to wait for the BIU to fetch a new instruction.There are threeconditions that will cause the EU to enter a 'wait' mode. The firstoccurs when an instruction requires access to a memory location not in thequeue. The BIU must suspend fetching instructions and output the address ofthis memory location.

After waiting for the memory access, the EU can resumeexecuting instruction codes from the queue (and the BIU can resume filling thequeue).The second conditionoccurs when the instruction to be executed is a 'jump' instruction.In this case control is to be transferred to a new ( nonsequential)address. The queue, however, assumes that instructions will always be executedin sequence and thus will be holding the 'wrong' instruction codes.The EU must wait while the instruction at the jump address is fetched.

8086 Microprocessor In Hindi

Notethat any bytes presently in the queue must be discarded (they are overwritten).One other condition cancause the BIU to suspend fetching instructions. This occurs during execution ofinstructions that are slow to execute. For example, the instruction AAM (ASCIIAdjust for Multiplication) requires 83 clock cycles to complete. At four cyclesper instruction fetch, the queue will be completely filled during the executionof this single instruction. The BIU will thus have to wait for the EU to pullover one or two bytes from the queue before resuming the fetch cycle.A subtle advantage to thepipelined architecture should be mentioned. Because the next severalinstructions are usually in the queue, the BIU can access memory at a somewhat'leisurely' pace. This means that slow- memparts can be used without affecting overall system performance.PROGRAMING MODELAs a programmer of the8086 or 8088 you must become familiar with the various registers in the EU andBIU.The data group consistsof the accumulator and the BX, CX, and DX registers.

Note that each can beaccessed as a byte or a word. Thus BX refers to the 16-bit base register but BHrefers only to the higher 8 bits of this register. The data registers arenormally used for storing temporary results that will be acted on by subsequentinstructions.The pointer and indexgroup are all 16-bit registers (you cannot access the low or high bytes alone).These registers are used as memory pointers. Sometimes a pointer reg will be interpreted as pointing to a memory byte and atother times a memory word. As you will see, the 8086/88 always stores wordswith the high-order byte in the high-order word address.Register IP could beconsidered in the previous group, but this register has only one function -topoint to the next instruction to be fetched to the BIU. Register IP isphysically part of the BIU and not under direct control of the programmer asare the other pointer registers.Six of the flags arestatus indicators, reflecting properties of the result of the last arithmeticor logical instructions. The 8086/88 has several instructions that can be usedto transfer program control to a new memory location based on the state of theflags.Three of the flags can beset or reset directly by the programmer and are used to control the operationof the processor.

These are TF, IF, and DF.The final group ofregisters is called the segment group. These registers are used by the BIU todetermine the memory address output by the CPU when it is reading or writingfrom the memory unit. To fully understand these registers, we must first studythe way the 8086/88 divides its memory into segments.SEGMENTED MEMORYEven though the 8086 isconsidered a 16-bit processor, (it has a 16-bit data bus width) its memory isstill thought of in bytes.

At first this might seem a disadvantage:Why saddle a 16-bitmicroprocessor with an 8-bit memory?Actually, there are acouple of good reasons. First, it allows the processor to work on bytes as wellas words.

This is especially important with I/O devices such as printers,terminals, and modems, all of which are designed to transfer ASCII-encoded (7-or 8-bit) data.Second, many of the8086's (and 8088's) operation codes are single bytes. Other instructions mayrequire anywhere from two to seven bytes. By being able to access individualbytes, these odd-length instructions can be handled.We have already seen thatthe 8086/88 has a 20-bit address bus, allowing it to output 2 10, or1'048.576, different memory addresses. As you can see, 524.288 words can alsobe visualized.As mentioned, the 8086reads 16 bits from memory by simultaneously reading an odd-addressed byte andan even-addressed byte.

For this reason the 8086 organizes its memory into aneven-addressed bank and an odd-addressed bank.With regard to this, youmight wonder if all words must begin at an even address. Well, the answer isyes. However, there is a penalty to be paid. The CPU must perform two memoryread cycles: one to fetch the low-order byte and a second to fetch thehigh-order byte.

This slows down the processor but is transparent to theprogrammer.The last few paragraphsapply only to the 8086. The 8088 with its 8-bit data bus interfaces to the 1 MBof memory as a single bank. When it is necessary to access a word (whether onan even- or an odd-addressed boundary) two memory read (or write) cycles areperformed.

In effect, the 8088 pays a performance penalty with every wordaccess. Fortunately for the programmer, except for the slightly slowerperformance of the 8088, there is no difference between the two processors.MEMORY MAPStill another view of the8086/88 memory space could be as 16 64K-byte blocks beginning at hex address000000h and ending at address 0FFFFFh. This division into 64K-byte blocks is anarbitrary but convenient choice. This is because the most significant hex digitincrements by 1 with each additional block. That is, address 20000h is 65.536bytes higher in memory than address 10000h. Be sure to note that five hexdigits are required to represent a memory address.The diagram is called amemory map.

This is because, like a road map, it is a guide showing how thesystem memory is allocated. This type of information is vital to theprogrammer, who must know exactly where his or her programs can be safelyloaded.Note that some memorylocations are marked reserved and others dedicated. The dedicated locations areused for processing specific system interrupts and the reset function.

Intelhas also reserved several locations for future H/W and S/W products. If youmake use of these memory locations, you risk incompatibility with these futureproducts.SEGMENT REGISTERSWithin the 1 MB of memoryspace the 8086/88 defines four 64K-byte memory blocks called the code segment,stack segment, data segment, and extra segment. Each of these blocks of memoryis used differently by the processor.The code segment holdsthe program instruction codes. The data segment stores data for the program.The extra segment is an extra data segment (often used for shared data). Thestack segment is used to store interrupt and subroutine return addresses.You should realize thatthe concept of the segmented memory is a unique one. Older-generationmicroprocessors such as the 8-bit 8086 or Z-80 could access only one 64K-bytesegment.

This mean that the programs instruction, data and subroutine stack allhad to share the same memory. This limited the amount of memory available forthe program itself and led to disaster if the stack should happen to overwritethe data or program areas.The four segmentregisters (CS, DS, ES, and SS) are used to 'point' at location 0 (thebase address) of each segment. This is a little 'tricky' because thesegment registers are only 16 bits wide, but the memory address is 20 bitswide. The BIU takes care of this problem by appending four 0's to the low-orderbits of the segment register. In effect, this multiplies the segment registercontents by 16.The point to note is thatthe beginning segment address is not arbitrary -it must begin at an addressdivisible by 16. Another way if saying this is that the low-order hex digitmust be 0.Also note that the foursegments need not be defined separately.

Indeed, it is allowable for all foursegments to completely overlap (CS = DS = ES = SS).Memory locations notdefined to be within one of the current segments cannot be accessed by the8086/88 without first redefining one of the segment registers to include thatlocation. Thus at any given instant a maximum of 256 K (64K. 4) bytes ofmemory can be utilized. As we will see, the contents of the segment registerscan only be specified via S/W. As you might imagine, instructions to load theseregisters should be among the first given in any 8086/88 program.LOGICAL AND PHYSICALADDRESSAddresses within asegment can range from address 00000h to address 0FFFFh.

This corresponds tothe 64K-byte length of the segment. An address within a segment is called anoffset or logical address. A logical address gives the displacement from theaddress base of the segment to the desired location within it, as opposed toits 'real' address, which maps directly anywhere into the 1 MB memoryspace. This 'real' address is called the physical address.What is the difference betweenthe physical and the logical address?The physical address is20 bits long and corresponds to the actual binary code output by the BIU on theaddress bus lines. The logical address is an offset from location 0 of a givensegment.When two segments overlapit is certainly possible for two different logical addresses to map to the samephysical address. This can have disastrous results when the data begins tooverwrite the subroutine stack area, or vice versa.

For this reason you must bevery careful when segments are allowed to overlap.You should also becareful when writing addresses on paper to do so clearly. To specify thelogical address XXXX in the stack segment, use the convention SS:XXXX, which is equal to SS.

16 + XXXX.ADVANTAGES OFSEGMENTED MEMORYSegmented memory can seemconfusing at first. What you must remember is that the program op-codes will befetched from the code segment, while program data variables will be stored inthe data and extra segments. Stack operations use registers BP or SP and thestack segment. As we begin writing programs the consequences of thesedefinitions will become clearer.An immediate advantage ofhaving separate data and code segments is that one program can work on severaldifferent sets of data. This is done by reloading register DS to point to thenew data. Perhaps the greatest advantage of segmented memory is that programsthat reference logical addresses only can be loaded and run anywhere in memory.This is because the logical addresses always range from 00000h to 0FFFFh,independent of the code segment base.

Such programs are said to be relocatable, meaning that they will run at any location inmemory. The requirements for writing relocatableprograms are that no references be made to physical addresses, and no changesto the segment registers are allowed.REFERENCEBooksThe 80x86 IBM PC and Compatible Computers ( Vol 1 and Vol 2)Microcomputer Systems: The 8086/8088 FamilyOnlineMaterialsIntel Developers website –AIX-86 (8086) Datasheet 8086 Architecture.

As 8086 does 2-stage pipelining (overlapping fetching and execution), its architecture is divided into two units:. Bus Interfacing Unit (BIU). Execution Unit (EU)Bus Interfacing Unit (BIU)-.

It provides the interface of 8086 to external memory and I/O devices. It operates with respect to bus cycles (machine cycles).

This means it performs various machine cycles such as memory read, I/O read etc. To transfer data with memory and I/O devices. BIU performs the following functions-. It generates the 20 bit physical address for memory access. It fetches instruction from memory. It transfers data to and from the memory and I/O.

It supports pipelining using the 6 byte instruction queue.The main components of the BIU are as follows:.Segment registers-. CS register: CS holds the base address for the Code Segment. All programs are stored in the Code Segment.

CS is multiplied by 10H to give the 20 bit physical address of the Code Segment. If CS = 4321H then CS x 10H = 43210H→ Starting address of Code Segment.

DS register: DS holds the base address for the Data Segment. It is multiplied by 10H to give the 20 bit physical address of the Data Segment.

If DS = 4321H then DS x 10H = 43210H→ Starting address of Data Segment. SS register: SS holds the base address for the Stack Segment. It is multiplied by 10H to give the 20 bit physical address of the Stack Segment. If SS = 4321H then SS x 10H = 43210H→ Starting address of Stack Segment.

ES register: ES holds the base address for the Extra Segment. It is multiplied by 10H to give the 20 bit physical address of the Extra Segment. If ES = 4321H then ES x 10H = 43210H→ Starting address of Code Segment.Instruction Pointer (IP)-.

It is a 16 bit register. It holds offset of the next instructions in the Code Segment. Address of the next instruction is calculated as CS x 10H + IP. IP is incremented after every instruction byte is fetched. IP gets a new value whenever a branch occurs.Address Generation Circuit-.

The BIU has a Physical Address Generation Circuit. It generates the 20 bit physical address using Segment and Offset addresses using the formula:Physical Address = Segment Address x 10H + Offset Address.6 Byte Pre-fetch Queue-.

It is a 6 byte first in first out (FIFO) RAM used to implement pipelining. Fetching the next instruction while executing the current instruction is called pipelining. BIU fetches the next six instruction bytes from the Code Segment and stores it into the queue. Execution Unit (EU) removes instructions from the queue and executes them. The queue is refilled when at least two bytes are empty as 8086 has a 16 bit data bus.